Чиплеты – упакованные в общий корпус формально независимые СБИС, которые тем не менее взаимодействуют по сверхскоростным шинам внутри этого корпуса и потому вполне заслуживают именоваться единой микросхемой.

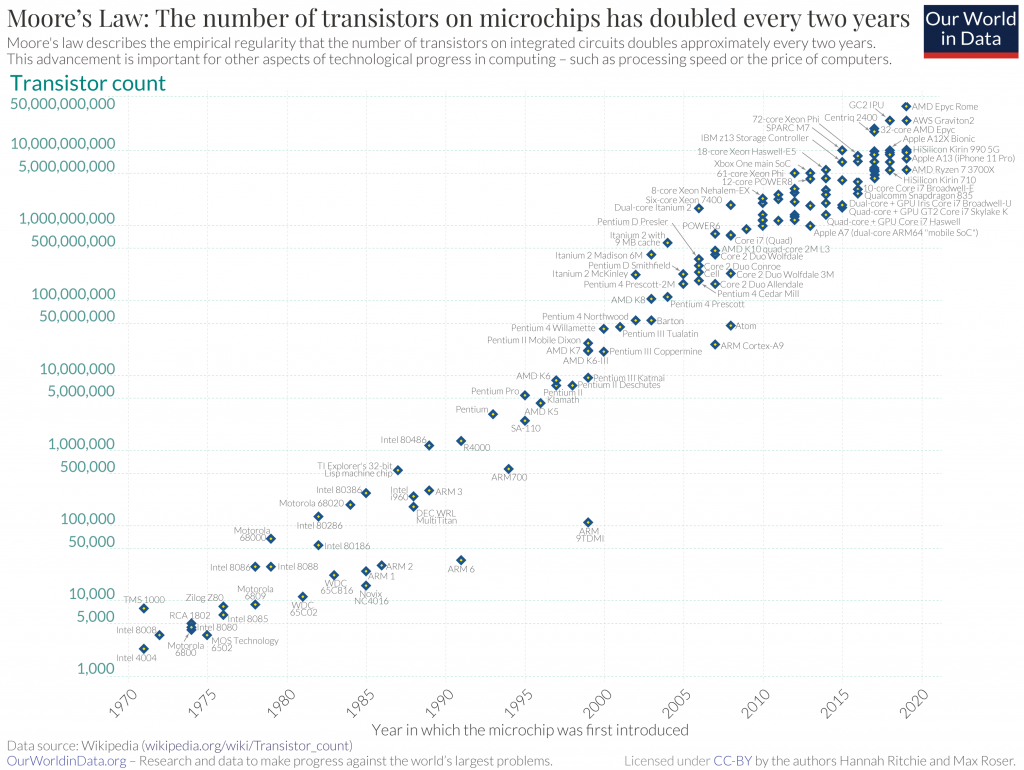

Эмпирическое правило, сформулированное еще в 1960-х Гордоном Муром, впоследствии главой Intel, в интерпретации последних десятилетий звучит так: «Каждые два года число транзисторов на интегральной микросхеме удваивается». И действительно, с очень неплохой точностью это правило выполняется до сих пор.

График с датами выпуска отдельных микрочипов и числом транзисторов на них и в самом деле, представляет собой почти прямую линию.

Правда, на этот закон теперь работает не только продолжающаяся миниатюризация технологических норм (сегодня уже выпускаются 3-нм СБИС), но и слияние прежде разрозненных микросхем воедино. В смартфоны, да и во многие ноутбуки теперь устанавливают уже не ЦП, ГП, сетевой контроллер и иные чипы по отдельности, а единые системы-на-кристалле с расширенной функциональностью (и, соответственно, гораздо бóльшим числом транзисторов).

Новой же опорой для продления действия закона Мура еще на какое-то число лет, если не десятилетий, обещают стать чиплеты – упакованные в общий корпус формально независимые СБИС, которые тем не менее взаимодействуют по сверхскоростным шинам внутри этого корпуса и потому вполне заслуживают именоваться единой микросхемой. Соответственно, число транзисторов внутри корпуса чиплета, подсчитанное как сумма числа транзисторов для каждой из составляющих его микросхем, имеет все шансы подчиняться закону Мура сравнительно долгое время.

Правда, для обеспечения высокоэффективного взаимодействия между составными элементами чиплетов придется решить ряд технологических проблем. На это нацелены наиболее передовые технологии, создаваемые TSMC (3DFabric и CoWos), Alchip (APLink die-to-die (D2D) I/0) и рядом других ведущих микропроцессорных разработчиков. В частности, как раз APLink D2D отвечает за высокоскоростной обмен между чиплетами по внутренней шине. Первая версия этой технологии соединяет выполненные по 12-нм технологическим нормам элементы шиной с пропускной способностью 1 Гбит/с, APLink D2D 2.0 имеет дело с 7-нм элементами и шиной 4 Гбит/с, а версия 3.0 обеспечит актуальным на сегодня фрагментам чиплетов канал обмена данными шириной в 16 Гбит/с.

В настоящее время инженеры Alchip трудятся над технологией APLink D2D 4.0, ориентированной на соединение 3-нм СБИС также по 16-Гбит/с шине, но с минимальными – не более 5 нс – задержками при передаче сигнала. Реализация такой шины для чиплетов, состоящих из микросхем, выполненных по самым миниатюрным на данный момент техпроцессам, позволит уверенно одолеть очередную ступень эмпирического закона Мура. А в перспективе Alchip и/или ее конкуренты наверняка предложат еще более скоростные и низколатентные внутрикорпусные шины обмена.