Компания TSMC объявила, что готова запустить массовое серийное производство микросхем по технологическим нормам А16 уже к концу 2026 г. В этом техпроцессе использована фирменная разработка TSMC – сеть электропитания Super Power Rail backside power delivery network, в которой транзисторы получают питание по шинам, расположенным с обратной стороны кремниевой подложки.

Тайваньская TSMC, получив от американской администрации в рамках CHIPS Act 6,6 млрд долл. (при том что финансирование Intel по линии этого законопроекта намереваются урезать с обещанных ранее 8,5 млрд долл. до менее чем 8 млрд, по причине далеко не выдающихся чипмейкерских достижений), похоже, преисполнилась уверенности в своих силах – и объявила в ходе недавнего мероприятия European Open Innovation Platform Ecosystem Forum в Амстердаме о готовности запустить массовое серийное производство микросхем по технологическим нормам А16 всего через пару лет, ближе к концу 2026-го.

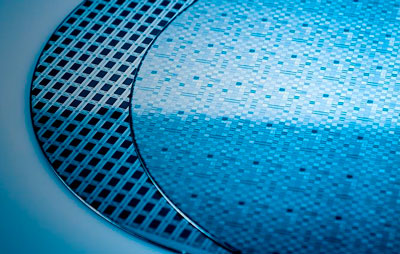

Производственный норматив A16 (маркетинговые «16 ангстрем», т. е. «1,6 нм») должен стать следующим по степени миниатюризации после уже практически освоенного тайваньцами N2 (маркетинговые же «2 нм»). В чисто геометрическом плане переход от N2 к A16 не представляется прорывным: ожидаемая плотность размещения транзисторов для последнего всего в 1,07–1,10 раз выше, чем для первого. Однако в случае A16 транзисторы того же типа (GAAFET), что и в техпроцессе N2, получают питание по шинам, расположенным с обратной стороны кремниевой подложки – обратной по отношению к той, на которой фотолитографическим способом формируются собственно полупроводниковые структуры: истоки, стоки и затворы транзисторов.

Тыльная сеть электропитания Super Power Rail backside power delivery network, BSPDN, – это фирменная разработка TSMC; она подразумевает подведение индивидуального контакта к истоку и стоку каждого транзистора с обратной стороны пластины-заготовки. И хотя она оказывается (по крайней мере, в теории) энергоэффективнее предложенной Intel подобной системы Power Via, но в то же время выходит сложнее и дороже в реализации.

Кроме того, от заказчиков, рассчитывающих на выпуск своих чипов по технологической норме A16, потребуется переработка инженерного дизайна микросхем по сравнению с привычной их компоновкой, когда шины подвода питания литографируются, как и логические межсоединения, на вышележащих слоях над транзисторными структурами. С учетом десятков, а то и сотен миллиардов транзисторов в современных передовых СБИС это крайне непростая задача, для решения которой бесспорно понадобится модернизация специализированного ПО инженерного дизайна.

Вдобавок появление слоев питающих шин на нижней стороне микросхем (а ведь слои логических межсоединений над уровнем транзисторов тоже никуда не денутся) затруднит как инспекцию готовых продуктов на предмет выявления производственных огрехов, так и отвод тепла от работающей под высокой нагрузкой СБИС. Однако у TSMC и ее партнеров есть по меньшей мере два года, чтобы справиться с этими вызовами. И в любом случае маловероятно, чтобы какой-то другой чипмейкер раньше этого срока смог предложить заказчикам сопоставимый по технической сложности и миниатюрности технологический процесс.