В версии Intel при производстве микросхем сеть энергоснабжающих межсоединений (PDN) переносится с фронтальной на тыльную сторону кремниевой пластины с максимальной утилизацией применяемых сейчас технологических процессов.

Миниатюризация технологических процессов, по которым производятся сверхсовременные СБИС, – процесс крайне дорогостоящий (особенно после перехода через предел 5–7 нм), однако совершенно необходимый для дальнейшего роста энергоэффективности вычислительных средств. Чем миниатюрнее транзистор, тем меньше энергии требуется для его активизации (перевода затвора из открытого состояния в закрытое и обратно). Следовательно, тем более сложные вычисления, задействующие больше транзисторов, становятся возможны в пределах прежнего энергобаланса: для наиболее актуальных приложений, таких как генеративный искусственный интеллект, это принципиально важно.

Традиционный фотолитографический процесс предполагает последовательное, послойное формирование на кремниевой подложке сперва полупроводниковых структур транзисторов, а затем соединяющих их в логические контуры металлических шин. Кроме того, необходимы и шины питания, по которым управляющее напряжение подается на затворы транзисторов. Величина этого напряжения – всего лишь порядка 1–2 В, однако с учетом того, что транзисторов на современных чипах десятки миллиардов, для их питания приходится оперировать довольно высокими токами – 10–20 А даже в случае смартфонных систем-на-кристалле, не говоря о еще более производительных компьютерных процессорах.

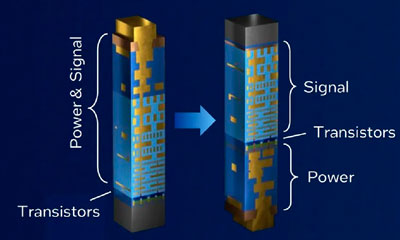

Слои с шинами питания формируются в ходе литографирования СБИС самыми последними, однако по вертикали эти межсоединения пронизывают всю толщу готовой структуры микросхемы, вплоть до кремниевого основания. И чем гуще расположены такие энергоснабжающие межсоединения (а с сокращением габаритов отдельного транзистора густота эта по необходимости возрастает), тем меньше остается в каждом горизонтальном слое пространства для формирования логических (сигнальных) связей между транзисторами – благодаря которым, собственно, и формируются вычислительные узлы, от самых базовых (логические вентили, сумматоры) до все более сложных.

Традиционная (слева) и перспективная, предполагающая заход с тыла, схемы подачи электропитания (power) на транзисторы (transistors) интегральной микросхемы. Источник: Intel.

Логичной в этой связи представляется идея перенести сеть энергоснабжающих межсоединений (power delivery network, PDN) с фронтальной стороны кремниевой пластины, на которой формируются транзисторы и контакты логических схем, на тыльную. Главный выигрыш от такого решения – значительное сокращение энергопотерь, поскольку, если не требуется совмещать сигнальные и электрические сети в одном слое, то контакты последних можно делать более крупными – а с ростом сечения проводника уменьшается его сопротивление.

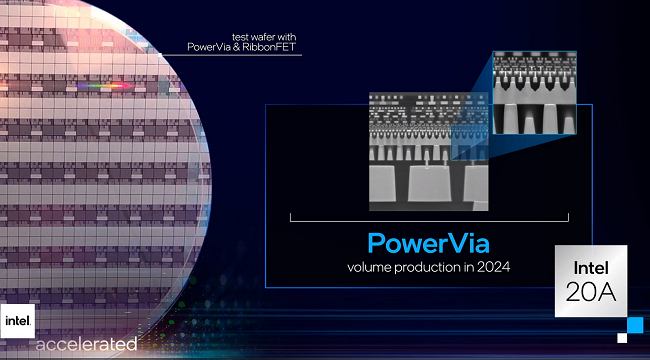

Разработчики из Intel предложили свою версию PDN под названием PowerVia, суть которой – в максимальной утилизации применяемых ныне технологических процессов. На первом этапе формирования новой СБИС все происходит привычным образом: на поверхности кремниевой пластины создаются транзисторные структуры, поверх которых слой за слоем наращивается сигнальная сеть логических межсоединений. Единственное различие в том, что рядом с этими структурами в кремнии сразу же протравливают довольно глубокие канавки, заполняемые затем металлом.

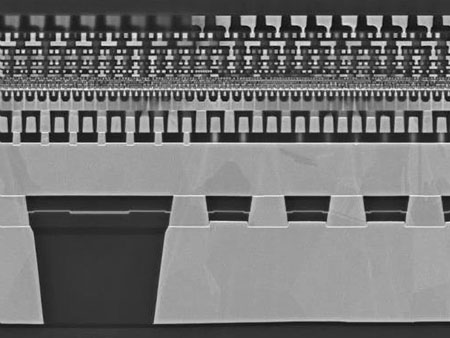

По завершении формирования сигнальных слоев на подготовленную таким образом кремниевую пластину укладывается другая, чистая; полученный «бутерброд» переворачивают, и основание первой пластины тщательно сошлифовывают – до тех пор, пока на поверхность не выйдут металлические контакты, полученные из упомянутых выше глубоких (в наноразмерном масштабе, конечно) канавок. И уже после этого на обратной поверхности перевернутой основной пластины создается – тоже вполне стандартным путем – PDN, позволяющая подводить питание к транзисторам с тыльной стороны (если фронтальной считать ту, на которой располагаются собственно полупроводниковые структуры и соединяющая их многослойная сигнальная сеть).

Микрофотография процессора с PowerVia в разрезе: сверху – слои сигнальной сети межсоединений (темные участки – металлические контакты, светлые – изолирующий диэлектрик), примерно на 1/3 высоты кадра от верхнего его обреза видна тонкая прерывистая светлая линия – слой кремния с транзисторными структурами на нем, ниже – U-образные контакты сети питания первого уровня, а еще ниже – слои PDN. Источник: Intel.

Безусловно, технология PowerVia, хотя и основана на хорошо отлаженных к настоящему времени процессах, бросает инженерам-микроэлектронщикам целый ряд серьезных вызовов: необходимо обеспечить бесперебойную работу транзисторов на гораздо более тонкой, чем прежде, кремниевой подложке; требуется организовать более уверенный отвод тепла от работающей СБИС (поскольку кремниевый слой теперь располагается в середине готового сэндвича); и даже процедура контроля качества изготавливаемых микросхем становится более трудозатратной – поскольку после формирования PDN на тыльной стороне прямой визуальный доступ к кремниевой пластине уже невозможен.

Тем не менее, овчинка стоит выделки: только за счет того, что в самом ближнем к транзисторам слое сигнальных межсоединений уже не нужно отводить пространство для размещения шин питания, среднее расстояние между сигнальными шинами в этом слое удается увеличить на 6 нм по сравнению с тем, которое характерно для классического техпроцесса Intel 4 (соответствует 7 нм в номенклатуре TSMC/Samsung Electronics). Это кажется невеликим достижением; однако именно этот слой межсоединений обходится в производстве дороже прочих (как раз по причине сверхминиатюрности формирующих его элементов), так что возможность чрезмерно не мельчить дает вполне изрядную экономию.

Как сообщили представители Intel на проходившем недавно в Токио мероприятии IEEE Symposium on VLSI Technology and Circuits, на данный момент выход годных кристаллов с пластины, литографированной по производственной норме Intel 4 PowerVia (т. е. с тыльным размещением слоев питания) уже соответствует тому, что был характерен для классического техпроцесса Intel 4 полугодовой давности. Вполне вероятно, что такими темпами компании удастся выполнить намеченную ранее задачу – и уже в 2024 г. начать серийный выпуск процессоров семейства Arrow Lake по производственным нормам Intel 20A (4 нм) уже сразу с PowerVia. TSMC, для сравнения, не планирует перемещать слои питания в изготавливаемых ею СБИС на тыльную сторону исходной пластины ранее 2026 г.